Nein, der Rest von uns muss mit dem Namen David Patterson nichts anfangen können. IT-Menschen, besonders solche, die mit Hardware zu tun haben, dagegen schon. Denn dieser Mann gehört zu den wichtigsten Computerarchitekten der vergangenen 60 Jahre. Als Person muss man ihn eine treue Seele nennen: von 1977 bis 2017 forschte und lehrte er an der University of California in Berkeley, und seit 1967 ist er mit seiner Jugendliebe verheiratet. Während viele andere Computerhelden eher Karriere in der freien Wirtschaft machten, blieb Patterson dem universitären Bereich erhalten, auch, weil er mit Leib und Seele Lehrer ist – fast alle, die bei ihm studiert haben, bezeichnen ihn als einen ihrer wichtigsten Einflüsse. So viel Stabilität ist in der Geschichte der Computerei selten. In der Szene wirklich bekannt geworden ist er als Mitentwickler der RISC-Architektur und als Co-Autor des RAID-Konzepts.

Die Älteren unter uns Digisauriern werden sich noch an die große Aufregung um die ersten kommerziell verfügbaren RISC-Prozessoren erinnern. Gemunkelt wurde ab etwa 1982, dass im CPU-Bau eine Revolution bevorstünde, die für erheblich schnellere Prozessoren sorgen würden. Es hieß, anstatt irgendwelchen Microcode von integrierten Speicherbausteinen anzusprechen, wäre der Befehlssatz eines RISC-Prozessors auf dem Chip festverdrahtet. Außerdem sei dieser Befehlssatz um ein Vielfaches kleiner, die Befehle selbst sehr, sehr einfach und deshalb schnell ausführbar.

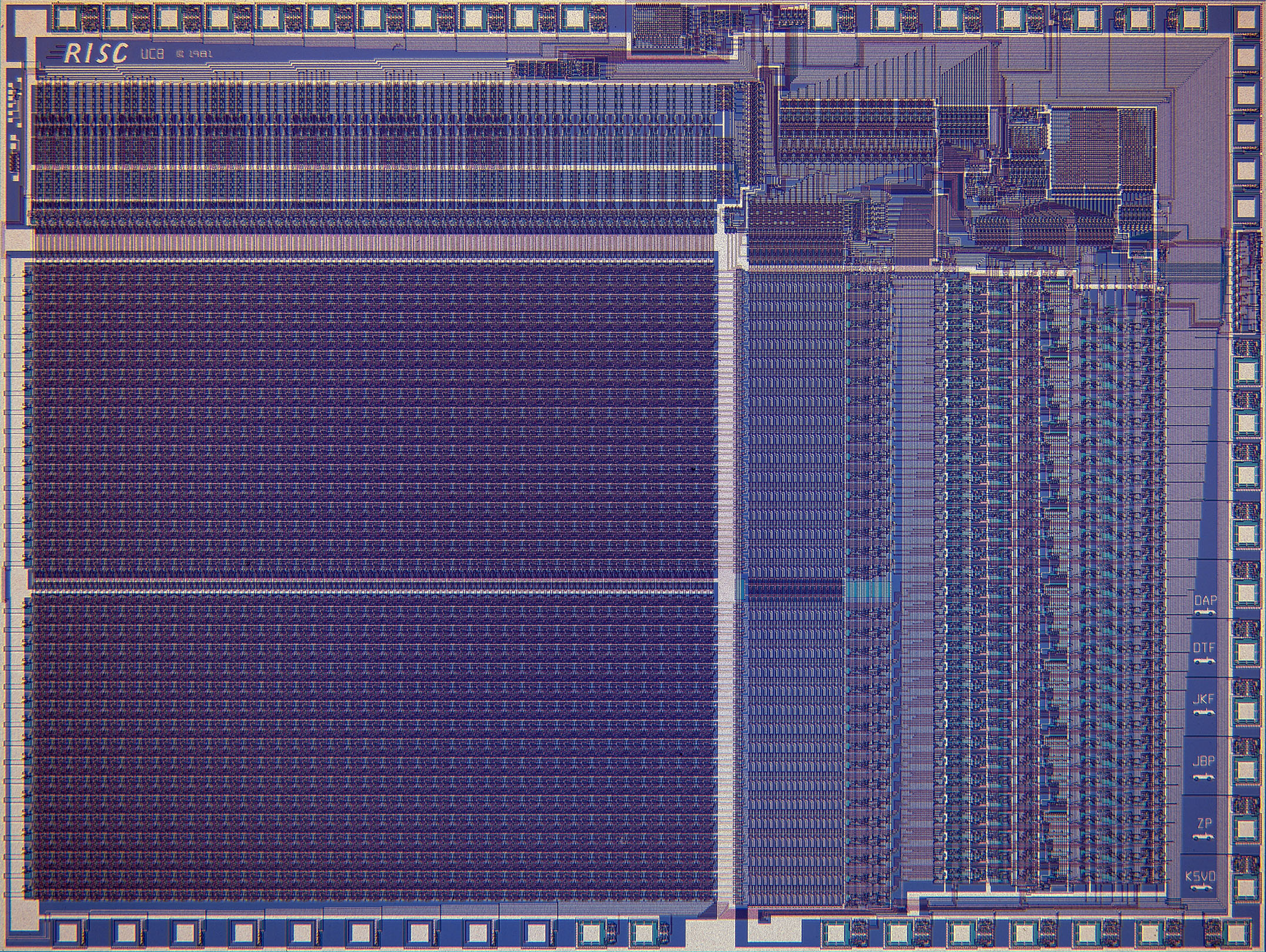

Ende der Sechzigerjahre hatte das Pentagon die IT als Schlüsseltechnologie auch für den militärischen Bereich erkannt, sodass die DARPA (Defense Advanced Research Projects Agency) auch die Hard- und Softwareforschung finanziell förderte. So entstand 1980 das Berkeley-RISC-Projekt, an dem David Patterson und Carlo H. Séquin federführend arbeiteten. Ziel war es in erster Linie, eine Architektur für die aufkommende Generation der VLSI-Chips (Very Large Scale Integration) zu entwickeln, also integrierten Schaltkreisen mit mindestens 10.000 Transistoren (bzw. Logikgattern). Die damalige militärische Führung versprach sich von dieser Technologie die Möglichkeit, Waffensysteme jeder Art mit integrierten Computern steuern zu können.

Zivile Programmierer dagegen freuten sich auf den Abschied von komplexen und hochabstrakten Maschinensprachen hin zu klugen Compilern, mit denen die Entwicklung von Anwendungen vereinfacht, beschleunigt und industrialisiert werden könnte. Heute sind ALLE Prozessoren in eingebetteten Systemen, also in Smartphones, Tablets und Smarthome-Komponenten RISC-Chips. Mit der ollen CISC-Technologie wäre die mobile Digitalisierung kaum möglich gewesen.

Was aber haben sich Patterson und Séquin konkret ausgedacht? Als Computerarchitekten haben sie zunächst weitestgehend theoretisch gearbeitet, also diskutiert und dokumentiert, wie einzelne Befehle grundsätzlich funktionieren sollten und dazu Regeln aufgestellt. Eine davon lautete: Kein Befehl soll mehr als einen Taktzyklus brauchen. Was wiederum zu einer strengen Abfolge der Operationen (Fetch, Decode, Load, Execute) führte und der grundsätzlichen Anforderung, die Befehle im Prozessor fest zu verdrahten – in einem integrierten Schaltkreis mit mindestens 10.000 Gattern kein Problem. Tatsächlich belegen die fest verdrahteten Befehlssätze auf RISC-Prozessoren heutiger Bauart weniger als 10 Prozent der Fläche.

Auf Basis dieses Konzepts, das sie 1981 als Paper mit dem Titel „Design and Implementation of RISC I“ (PDF-Link) veröffentlichten, entstand der erste Modellprozessor mit dem internen Namen „Gold“. In den folgenden zwei Jahren lief als zweites Projekt das „Blue“ genannte. Aber schon auf Basis des genannten Papers begannen Wissenschaftler, unter anderem in Großbritannien, mit der Entwicklung von RISC-Prozessoren für den kommerziellen Gebrauch. Schon 1983 hatte Sophie Wilson eine eigene RISC-Mikroprozessor-Architektur namens „Acorn Risc Machine“ (kurz: ARM) entwickelt, aber es dauerte bis 1987 bis die Firma Acorn, die zuvor durch den BBC-Mikro-Lerncomputer berühmt und reich geworden war, mit dem Acorn Archimedes den ersten Personal Computer mit einer RISC-CPU auf den Markt brachte.

Wie gesagt: Ohne das im erwähnten Papier niedergelegte Konzept wären vielleicht nie RISC-Prozessoren Realität geworden. Die Geschichte ging rasant weiter: Aus „Acorn Risc Machine“ wurde „Advanced Risc Machines“, und durch Auslagerung 1989 die eigenständige Firma ARM Limited, die heute der japanischen Softbank gehört und am Fließband Mikroprozessor-Designs entwickelt und an Hersteller von CPUs für eingebettete Systeme lizensiert.

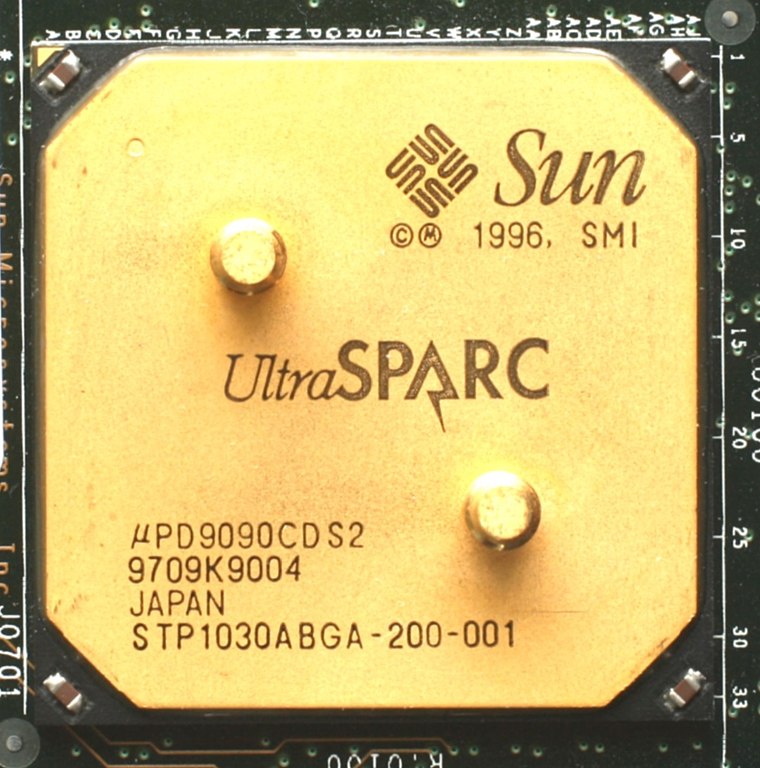

Die britische Hardwareschmiede Acorn bildete den einen Arm der RISC-Bewegung, Sun Microsystems aus Kalifornien mit den SPARC-Prozessoren ab 1985 den zweiten wichtigen. Tatsächlich aber arbeiteten ab 1983 fast alle einigermaßen wichtigen Chip-Hersteller an RISC-Prozessoren, auch Intel. Man überbot sich mit Ankündigungen, die CISC-Welt war schon tot bevor es überhaupt RISC-CPUs für persönliche Computer gab.

Den Begriff RISC hat David Patterson geprägt, er wurde aber ab etwa 1987 so inflationär verwendet, dass seine Bedeutung immer mehr verwässerte. Denn die Hersteller klebten überall das RISC-Label drauf, wenn ihr neuer Prozessor nicht mehr ganz so CISC war wie vorher. Heute, mehr als 30 Jahre nachdem VLSI eher die unterste Stufe der Integration bei Schaltkreisen ist, sind die Befehlssätze samt und sonders klein und festverdrahtet – alles ist RISC. Passend zum Thema hat Patterson zusammen mit dem Kollegen John Hennessey 1990 ein Buch mit dem Titel „Computer Architecture: A Quantitative Approach“ verfasst (das übrigens bis heute als absolutes Standardwerk zum Thema gilt).

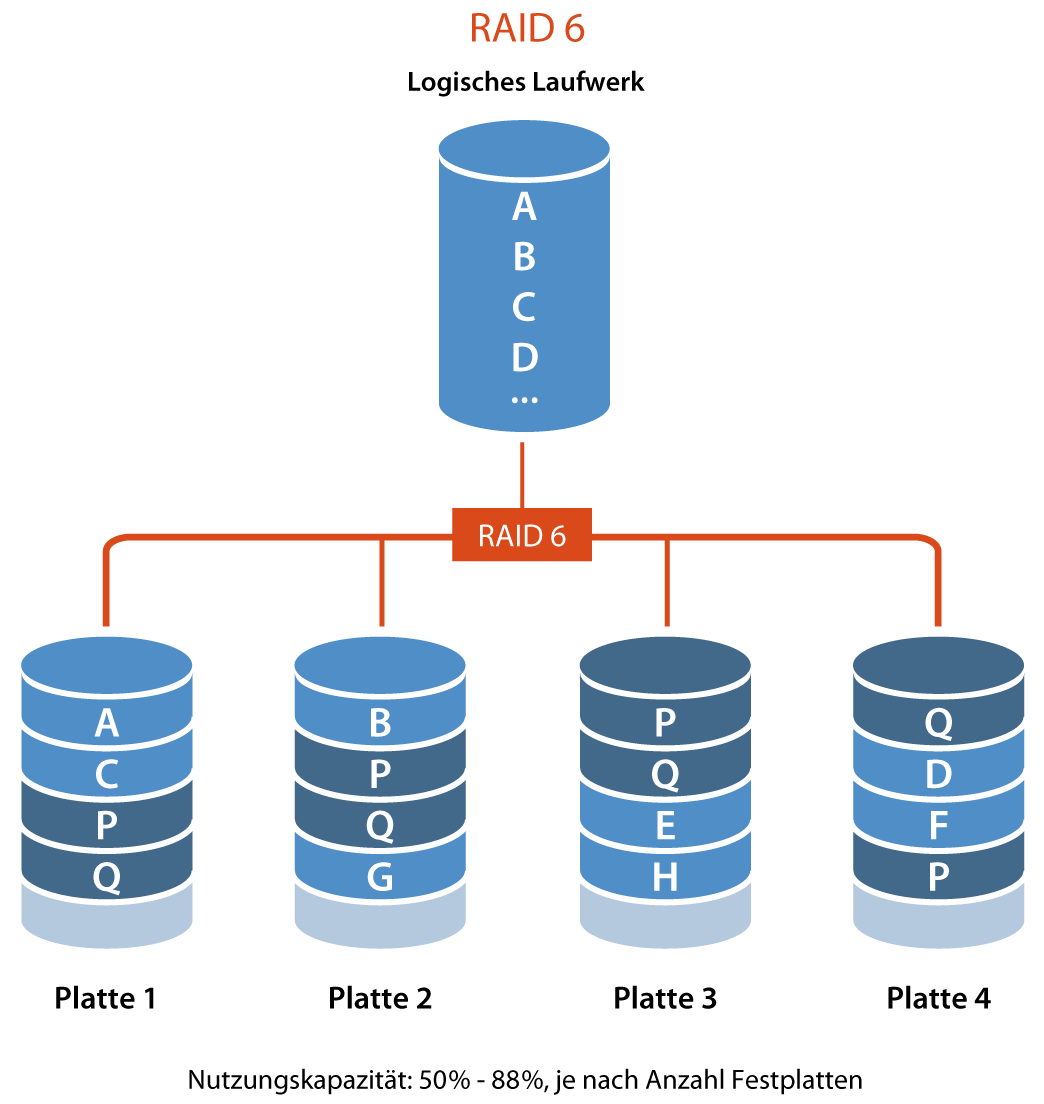

Weniger spektakulär ist Pattersons zweite große „Erfindung“ – dem „redundant array of independent disks“ (kurz: RAID). Die Idee dahinter ist, eine miteinander verbundene Anzahl Massenspeicher (Festplatten/HDs, SSDs) verwalten zu können wie ein einziges logisches Laufwerk – eine Technologie, die heutzutage vollständig standardisiert ist und überall da eingesetzt wird, wo große Datenmengen zu speichern sind. Der Clou an diesem Konzept, dass Patterson von 1989 bis 1993 zusammen mit dem Kollegen Randy Kratz entwickelte: Daten werden ganz bewusst redundant, also mehrfach und auf verschiedenen physikalischen Speichern gesichert, damit sie auch beim Ausfall einzelner Platten weiter verfügbar bleiben. Das hört sich trivial an, wenn man sich aber die aktuellen RAID-Spezifikationen anschaut, erkennt man, dass es gar nicht so einfach ist, die Balance zwischen Datensicherheit und Speichernutzung intelligent und automatisch zu erzielen.

Nach seiner Emeritierung konzentrierte sich David Patterson auf seine Ämter in diversen Verbänden und Kommissionen wie der Association for Computing Machinery (ACM), der IEEE, der National Academy of Sciences, der American Academy of Arts and Sciences und der National Academy of Engineering. Seit 2016 ist er zudem Distinguished Engineer bei Google, wo er beratend zu sämtlichen Zukunftsthemen der Computerindustrie und der Digitalisierung allgemein tätig ist. 2017 wurde er mit dem Turing Award ausgezeichnet, der als so etwas wie der Nobelpreis der Computerwissenschaften gilt.

Hier ein langes, hochinteressantes Gespräch aus dem Jahr 2020 von Lex Fridman mit David Patterson über die Geschichte und den Stand der Technik bei Computerarchitekturen.